### Rechnerstrukturen

Vorlesung im Sommersemester 2007

Prof. Dr. Wolfgang Karl

Universität Karlsruhe (TH)

Fakultät für Informatik

Institut für Technische Informatik

### Vorlesung Rechnerstrukturen

Kapitel 2: Parallelismus auf Befehlsebene

2.3: Nebenläufigkeit, VLIW, EPIC

- EPIC: Explicitly Parallel Instruction Computing

- Gemeinsames Projekt von Hewlett-Packard und Intel (1994 angekündigt)

- Ziele:

- 64 Bit Architektur: IA-64

- Explizite Spezifikation des Parallelismus im Maschinencode: EPIC-Format, (entspricht VLIW-Prinzip)

- Bedingte Ausführung von Befehlen (Predication)

- Spekulative Ausführung von Ladeoperationen (Data Speculation)

- Großer Registersatz

- Skalierbarer Befehlssatz

- Sinnvolles Zusammenwirken zwischen Compiler und Hardware

- Itanium: erster Prozessor der P7-Generation (Code-Name Merced)

### • Intel IA-64

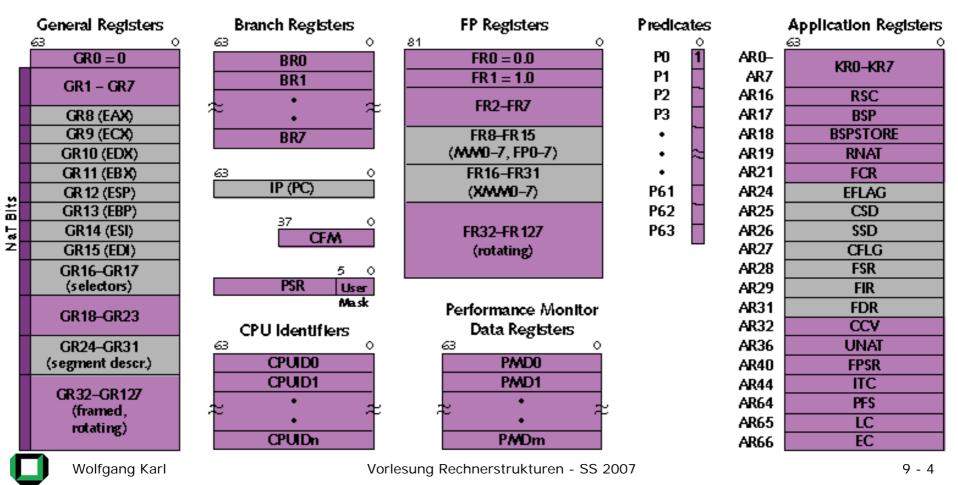

### Registersatz

Quelle: Microprocessor Report, Vol.13, Nr.7, 1999

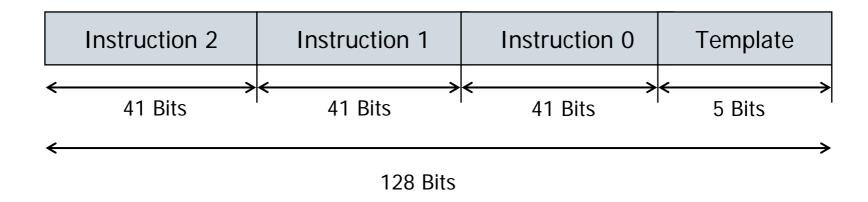

### IA-64 ISA: Befehlsformat

- Opcode

- Predicate

- 2 Felder für Quelloperandenregister

- 1 Feld für Zielregister

#### IA-64 ISA

– IA-64 Instruktionen werden vom Compiler in so genannte Bundles gepackt

#### IA-64 ISA

#### - Bundles:

- Template: zeigt explizit an, ob

- die Instruktionen im Bundle gleichzeitig ausgeführt werden dürfen, oder

- eine oder mehrere Instruktionen sequentiell auszuführen sind, oder

- benachbarte Bundles parallel ausgeführt werden können.

### Beispiele von Befehlsgruppen:

```

.mii

add r1 = r2,r3

sub r4 = r4, r5;;

shr r7 = r4, r12;;

Gruppe

.mmi

1d8 r2 = [r1];;

st8 [r1] = r23

tbit p1,p2 = r4,5

.mbb

1d8 r45 = [r55]

br.call b1 =func1

(p3)

br.cond Label1

(p4)

.mfi

st4 [r45] = r6

fmac f1 = f2,f3

add r3 = r3,8;;

```

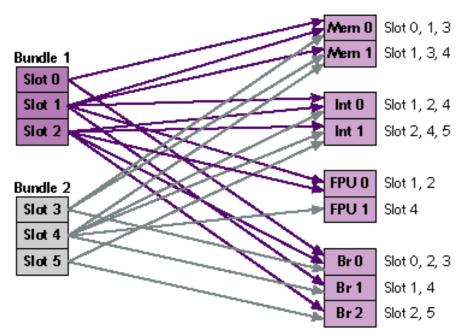

- Anstoßen der Befehle zur Ausführung

- Beispiel: Itanium

Es können bis zu sechs Instruktionen pro Takt zur Ausführung angestoßen werden. Die Instruktionen kommen von zwei Bundles. Jeder Bundle hat 3 Slots.

#### IA-64: Skalierbarkeit

- Jedes Bundle enthält drei Instruktionen für eine Menge von drei Funktionseinheiten.

- Ein IA-64 Prozessor kann n Mengen von jeweils drei Funktionseinheiten haben, welche die Informationen im Template nutzen, dann können mehrere Bundles in ein Instruktionswort mit der Länge n Bundles gepackt werden.

- → Skalierbarkeit bezüglich der Anzahl der Funktionseinheiten

- Predication, bedingte Befehlsausführung

- Beispiel:

#### Bedingte Befehlsfolge

- Evaluierung der bedingten Ausdrücke mit Hilfe von Compare-Operationen.

- Jeder Befehl hat ein 6 Bit breites Predicate Feld zur Angabe des Predicate-Registers

- Elimination von Sprüngen

## Predication (Bedingte Befehlsausführung)

- Zur Laufzeit werden die voneinander unabhängigen Befehle zur Ausführung angestoßen.

- Der Prozessor führt die Befehle auf den möglichen Programmverzweigungen aus, aber speichert die Ergebnisse nicht endgültig.

- Überprüfen der Predicate Register

- Falls das Register eine 1 enthält, dann ist wird die Ausführung der Instruktion abgeschlossen.

- Falls das Register eine 0 enthält, dann wird das Ergebnis verworfen.

# IA-64 Control Speculation

Problem: Verzweigungen schränken Code-Verschiebungen ein

Ladeoperation kann nicht über den Sprung verschoben werden, denn es könnten Alarme ausgelöst werden.

# IA-64 Control Speculation

Lösung: Spekulative Operationen, die keine Alarme auslösen

```

instA

instB

...

br Grenze

ld8 r1 =[r2]

use r1

```

```

Spekulative Ladeoperation

ld8.s r1 =[r2]

use r1

instA

instB

...

br

Chk.s Speculation Check

```

# IA-64 Control Speculation

- Einführung von spekulativen Ladeoperationen

- Verursachen keinen Alarm:

- Falls zur Laufzeit die Operation einen Alarm auslöst, dann wird dieser Alarm verzögert

- Setzen von NaT-Bit (Deferred Exception Token, Not-a-Thing Bit) in Zielregister

- Spekulative Ladeoperation kann über Verzweigungen hinweg verschoben werden

- Einfügen von Speculation Check Instruktion (chk.s) anstelle der Ladeoperation

- Zur Laufzeit überprüft die Check-Operation das Zielregister, ob NaT gesetzt ist. Wenn ja, dann erfolgt eine Verzweigung zu einem speziellen Fix-up-Code.

Problem: Zeiger können Compiler zu konservativen Annahmen über die Referenzen zwingen, was eine Code-Verschiebung verhindert.

```

instA

instB

...

store

```

Ladeoperation kann nicht über den die Speicheroperation verschoben werden, da beide dieselbe Adresse referenzieren können.

Lösung: Vorgezogene Ladeoperationen

```

instA

instB

...

store

```

```

ld8 r1 =[r2]

use r1

```

#### Vorgezogene Ladeoperation

```

ld8.a r1 =[r2]

use r1

instA

instB

...

store

```

chk.a

**Speculation Check**

- Lösung: Vorgezogene Ladeoperationen

- Verschieben von Lade-Operationen auch vor Speicher-Operationen.

- Vorgezogene Lade-Operation (ld.a)

- Zur Laufzeit werden Informationen (Zielregister, Speicheradresse, auf die zugegriffen wird, Zugriffsgröße) in Advanced Load Address Table (ALAT) festgehalten.

- Zur Laufzeit prüft die Hardware, wenn eine Speicheroperation ausgeführt wird, ob eine Adresse in der ALAT mit der Zugriffsadresse übereinstimmt. Wenn ja, dann wird der Eintrag in ALAT gelöscht

- Lösung: Vorgezogene Ladeoperationen

- Einfügen der Check-Operation (chk.a)

- Prüft, ob Eintrag von der entsprechenden vorgezogenen Ladeoperation in ALAT steht.

- Wenn nicht, dann hat es eine Kollission mit einer Speicheroperation gegeben und es erfolgt eine Verzweigung zu einem Fix-up-Code.

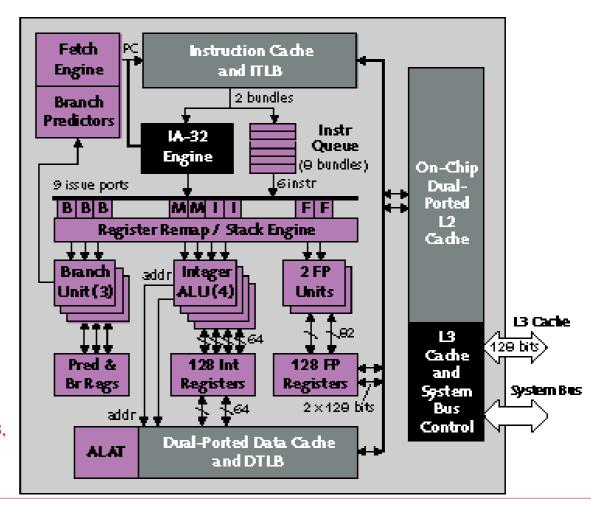

### Intel Itanium

Quelle: Microprocessor Report, Vol.13, Nr.13, October 5, 1999

#### Intel Itanium

- 64-Bit Prozessor der P7 Generation

- EPIC

- 10-stufige Pipeline mit 6 Befehlen, die gleichzeitig zur Ausführung angestoßen werden können.

- 128 GP- und 128 FP-Register keine

Registerumbenennung: rotierende Registerfenster

- Bedingte Befehlsausführung: 64 1 Bit Predicate Register

- 9 Funktionseinheiten

- Misprediction Penalty: 9 Zyklen

#### Intel Itanium

- Spekulative Ladeopationen

- 4-fach mengenassoziative L1 Befehls- und Daten-Cache-Speicher (Write-through)

- 6-fach mengenassoziativer L2 Cache (Copy-back)

- Informationen

- Intel: <a href="http://www.intel.com/">http://www.intel.com/</a>

- Intel Technology Journal: http://developer.intel.com/technology/itj

- IEEE Micro: Sonderheft im Spe./Okt. 2000

- Henn./Patt.: Computer Architecture: Kap. 4.7

#### • Literatur:

- Brinkschulte/Ungerer: Mikrocontroller und Mikroprozessoren. Springer-Verlag, 2002: Kap. 6.1-6.4, Kap. 7

- Hennessy/Patterson: Computer ArchitectureA Quantative Approach. 3. Auflage: Kap.

### Vorlesung Rechnerstrukturen

Kapitel 2: Parallelismus auf Befehlsebene

2.4: Thread-Level Parallelismus, Multithreading

- Grundsätzliche Aufgabe beim Prozessorentwurf:

- Reduzierung der Untätigkeits- oder Latenzzeiten

- Entstehen bei Speicherzugriffen, insbesondere bei Cache-Fehlzugriffen

- Bei speichergekoppelten Multiprozessoren, wenn auf nicht-lokalen Speicher zugegriffen wird

- Synchronisation von parallelen Kontrollfäden (Threads)

- Lösung: parallele Ausführung mehrerer

Kontrollfäden

- Mehrfädige Prozessortechnik

- Gegeben mehrere ausführbereite Kontrollfäden, Threads

- Ziel: Parallele Ausführung mehrerer Kontrollfäden

- Voraussetzung:

- Mehrere Kontrollfäden sind geladen

- Kontext muss für jeden Thread gesichert werden können

- Mehrere getrennte Registersätze auf Prozessorchip

- Mehrere Befehlszähler

- Getrennte Seitentabellen

- Threadwechsel, wenn gewartet werden muss

- Mehrfädige Prozessortechnik

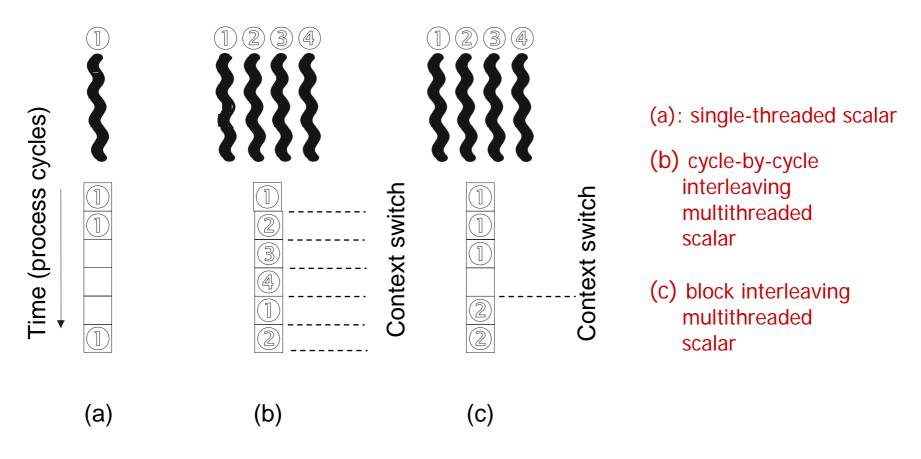

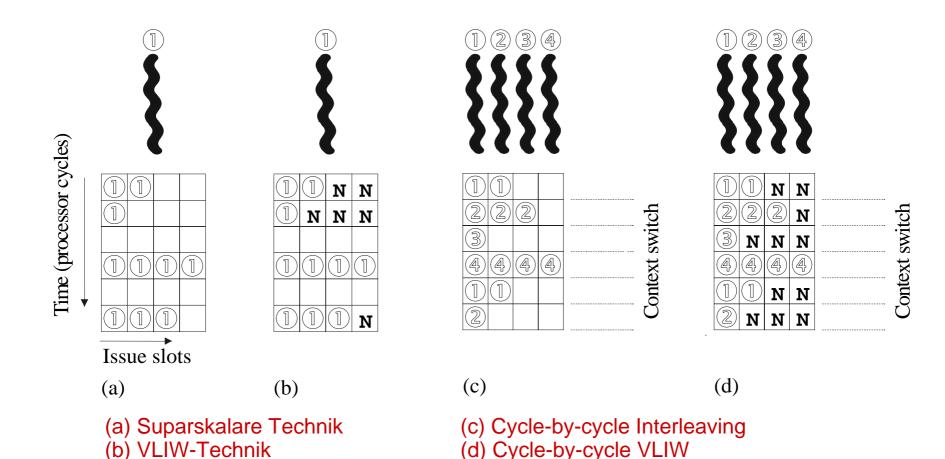

- Cycle-by-cycle Interleaving (feingranulares Multithreading)

- Eine Anzahl von Kontrollfäden ist geladen.

- Der Prozessor wählt in jedem Takt einen der ausführungsbereiten Kontrollfäden aus.

- Der nächste Befehle in der Befehlsreihenfolge des ausgewählten Kontrollfadens wird zur Ausführung ausgewählt.

- Beispiele

- Multiprozessorsysteme HEP, Tera

- Nachteil:

- Die Verarbeitung eines Threads kann erheblich verlangsamt werden, wenn er ohne Wartezeiten ausgeführt werden kann

# Mehrfädige Prozessortechnik

### - Block Interleaving

Befehle eines Kontrollfadens werden so lange ausgeführt, bis eine Instruktion mit einer langen Latenzzeit ausgeführt wird. Dann wird zu einem anderen ausführbaren Kontrollfaden gewechselt.

#### • Vorteil:

Die Bearbeitung eines Threads wird nicht verlangsamt, da beim Warten ausführungsbereiter Thread gestartet wird

#### Nachteil:

- Bei Thread-Wechsel Leeren und Neustarten der Pipeline,

- Nur bei langen Wartezeiten sinnvoll

# Mehrfädige Prozessortechnik

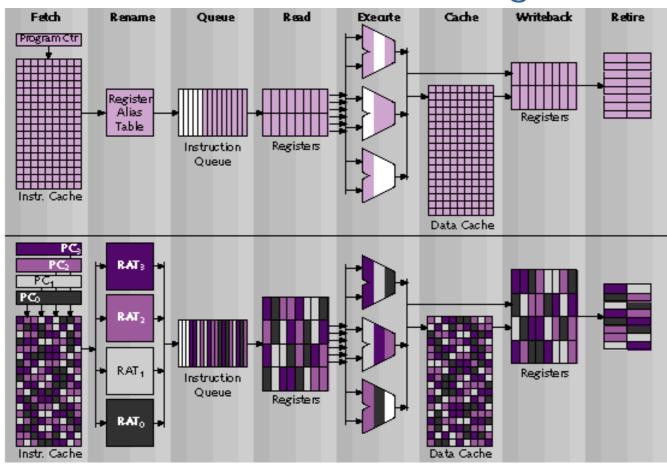

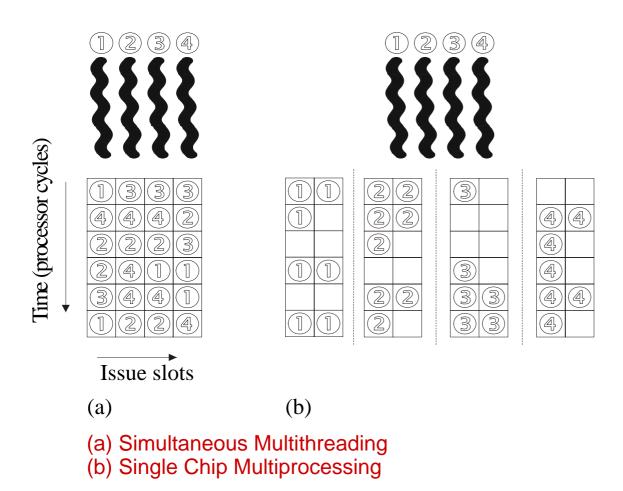

- Simultaneous Multithreading

- Mehrfach superskalarer Prozessor

- Die Ausführungseinheiten werden über eine Zuordnungseinheit aus mehreren Befehlspuffern versorgt.

- Jeder Befehlspuffer stellt einen anderen Befehlsstrom dar.

- Jedem Befehlsstrom ist eigener Registersatz zugeordnet.

- Mehrfädige Prozessortechnik

- Simultaneous Multithreading

- Mehrfädige Prozessortechnik

- Simultaneous Multithreading: Diskussion

- Abwägen zwischen Geschwindigkeit eines Threads und dem Durchsatz vieler Threads

- Ein bevorzugter Thread

- » Allerdings kann dies auf Kosten des Durchsatzes gehen, da Befehle anderer Threads möglicherweise nicht bereit stehen

- Mischen vieler Threads:

- » Geht möglicherweise zu Lasten der Leistung der einzelnen Threads

- Mehrfädige Prozessortechnik

- Simultaneous Multithreading: Beispiele

- Compaq Alpha 21464 (EV8), ursprünglich angekündigt für 2002/2003, Entwicklung aber eingestellt! Entwicklergruppe jetzt bei Intel

- Intel P4: Hyperthreading

- Sun Ultra SPARC IV: Chip Multithreading

### Multithreading

#### Literatur:

Brinkschulte, U.; Ungerer, T.:

Microcontroller und Mikroprozessoren.

Springer, Heidelberg, 2002: Kap.: 10.4.3

### Zusammenfassung

# Vergleich von Prozessortechniken

(siehe Brinkschulte, Ungerer: Mikrocontroller und Mikroprozessoren: Kap. 10.4.3)

# Vergleich von Prozessortechniken

# Vergleich von Prozessortechniken

# Zusammenfassung

- Architektur und Mikroarchitektur von Prozessoren

- Architektur

- -RISC-Prinzip: Pipelining

- Superskalare Prozessortechnik

- -VLIW/EPIC

- Multithreading

- Vergleich

# Vorlesung Rechnerstrukturen

Kapitel 3: Multiprozessoren – Parallelismus auf Prozess/Thread-Ebene

3.1: Motivation

### Überblick

- Allgemeine Grundlagen, parallele

Programmierung, Verbindungsstrukturen,

Leistungsfähigkeit

- Speichergekoppelte Multiprozessoren: SMP und DSM, Cache-Kohärenz und Speicherkonsistenz, Rechnerbeispiele

- Nachrichtengekoppelte Multiprozessoren,

Beispielrechner

- Einordnung:

- Klassifikation nach Flynn: MIMD-Rechner

- Warum Multiprozessorsysteme?

- Hohe Anforderungen von Anwendungen an die Rechenleistung

- Technisch-wissenschaftlicher Bereich

- Rechnergestützte Simulation

- Kommerzieller Bereich

- Server, Datenbank-Anwendungen, WEB

#### Motivation

- Hohe Anforderungen von Anwendungen an die Rechenleistung

- Beispiel technisch-wissenschaftlicher Bereich

- C Rechnergestützte Simulation

- Strömungsmechanik

- Modellierung der globalen klimatischen Veränderungen

- Evolution von Galaxien

- Struktur von Materialien

- **—** .....

- →Anforderung an die Rechenleistung: Bereich Tera-, bzw. Petaflop

"Grand Challenges"

- Hohe Anforderungen von Anwendungen an die Rechenleistung

- Höchstleistungsrechner:

- TOP500-Liste

- Führt die schnellsten Rechner der Welt auf

- Erscheint immer im Juni und im November eines Jahres

- http://www.top500.org

- » Beispiel: TOP500 Liste (November 2005)

#### Motivation

- Höchstleistungsrechner:

- TOP500-Liste

- Nr.1: BlueGene/L, Modell: eServer Blue Gene Solution

- Standort: DOE/NNSA/LLNL

- Anzahl Prozessoren: 132072 (!)

- Leistung: 280600 GFLOPS (Linpack)

– Anwendung: Protein-Faltung

Quelle: IBM Research;

http://www.research.ibm.com/bluegene/sciapp.html

#### Motivation

- Höchstleistungsrechner:

- BlueGene/L DD2 beta-System (0.7 GHz PowerPC 440)

- Bilder der Fertigung:

Quelle: IBM Research;

http://domino.research.ibm.com/comm/pr.nsf/pages/rsc.bluegene\_2004.html

#### Motivation

- Höchstleistungsrechner:

- BlueGene/L DD2 beta-System (0.7 GHz PowerPC 440)

- Fertiges System:

Quelle: IBM Research;

http://domino.research.ibm.com/comm/pr.nsf/pages/rsc.bluegene\_2004.html

#### Motivation

- Höchstleistungsrechner:

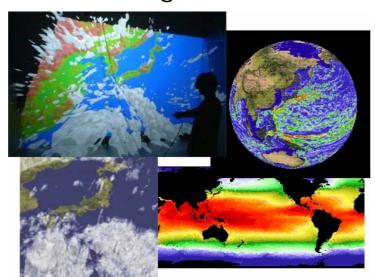

- Earth Simulator (Japan, Platz 7 (TOP500, Nov. 05)

- Anzahl Prozessoren: 5120

- Leistung: 35,86 TFLOPS (Linpack),

- Anwendung: Klimaforschung

Quelle: The Earth Simulator Center;

- Höchstleistungsrechner:

- Earth Simulator (Japan, Platz 7 (TOP500, Nov. 05)

- Ziel des Earth Simulator Project:

- » "The Earth Simulator Project will create a "virtual earth" on a supercomputer to show what the world will look like in the future by means of advanced numerical simulation technology."

- » "Achievement of high-speed numerical simulations with processing speed of 1000 times higher than that of the most frequently used supercomputers in 1996."

- Höchstleistungsrechner:

- Earth Simulator (Japan, Platz 7 (TOP500, Nov. 05)

- "Understanding and Prediction of Global Climate Change

- » Occurrence prediction of meteorological disaster

- » Occurrence prediction of El Niño

- » Understanding of effect of global warming

- » Establishment of simulation technology with 1km resolution"

- Höchstleistungsrechner:

- Earth Simulator (Japan, Platz 7 (TOP500, Nov. 05)

- "Understanding of Plate Techtonics

- » Understanding of long-range crustal movements

- » Understanding of mechanism of seismicity

- » Understanding of migration of underground water and materials transfer in strata"

#### Motivation

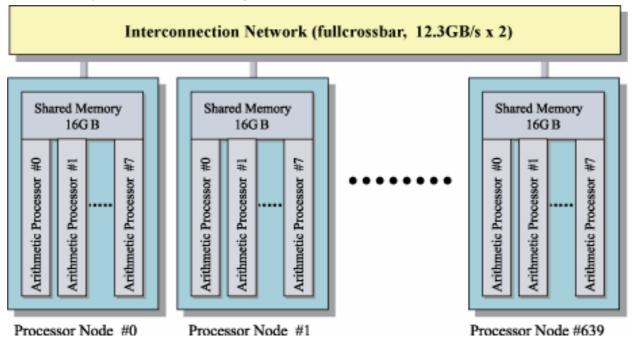

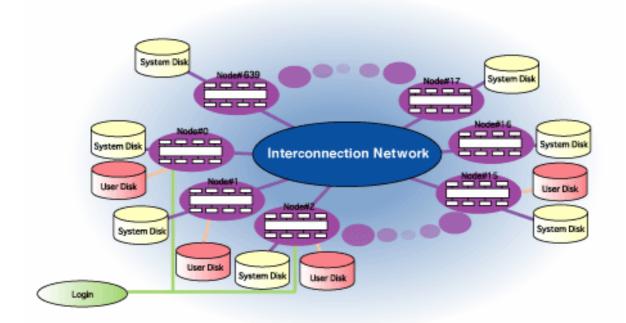

- Höchstleistungsrechner:

- Earth Simulator (Japan)

- Systemkonfiguration

Quelle: The Earth Simulator Center; http://www.es.jamstec.go.jp/esc/eng/Hardware/system.html

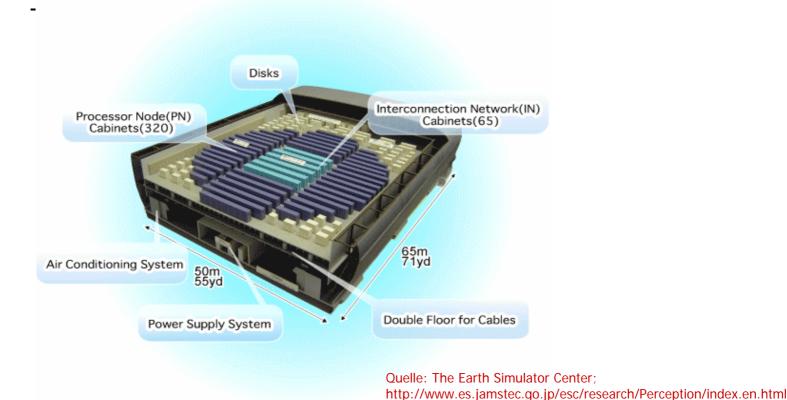

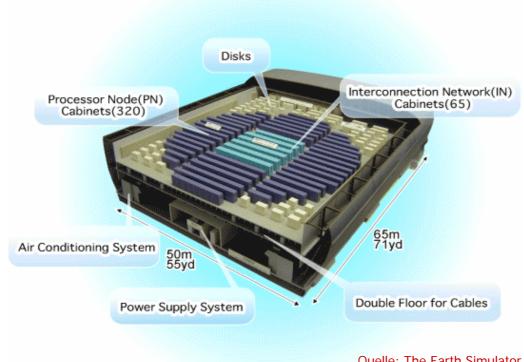

### Motivation

- Höchstleistungsrechner:

- Earth Simulator (Japan)

Quelle: The Earth Simulator Center;

http://www.es.jamstec.go.jp/esc/research/Perception/index.en.html

- Höchstleistungsrechner:

- Earth Simulator (Japan)

### Motivation

- Höchstleistungsrechner:

- Earth Simulator (Japan)

Quelle: The Earth Simulator Center;

http://www.es.jamstec.go.jp/esc/research/Perception/index.en.html

#### Motivation

- Höchstleistungsrechner:

- Earth Simulator (Japan)

Quelle: The Earth Simulator Center; http://www.es.jamstec.go.jp/esc/research/Perception/index.en.html

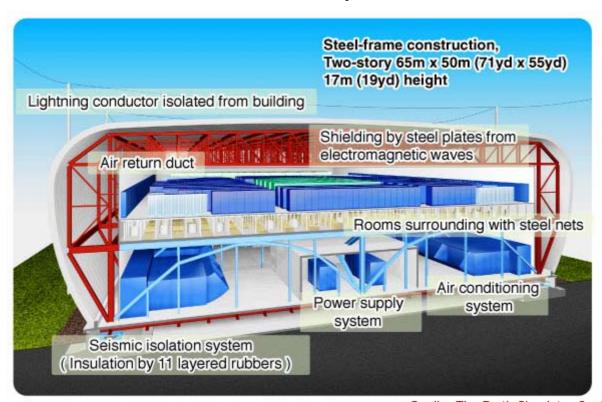

# Earth Simulator

Quelle: The Earth Simulator Center; http://www.es.jamstec.go.jp/esc/eng/GC/index.html

# Earth Simulator

- Earth Simulator

- Erdbebenschutz:

Quelle: The Earth Simulator Center; http://www.es.jamstec.go.jp/esc/research/Perception/index.en.html